模拟IC升级需要什么样的EDA工具支持?

更新时间:2019-09-25

链料网·找料的现货平台

IC设计离不开EDA工具的支持,模拟设计也不例外。在<电子发烧友>9月20日举行的2019年中国模拟半导体大会上,Cadence中国区技术支持总监栾志雨带来了主题为《中国模拟IC升级更需要借力EDA工具》的演讲,在本次演讲中,他阐述了针对16nm及以下节点工艺的模拟IC设计需要注意的问题。

图1:Cadence中国区技术支持总监栾志雨。

流程规范化

目前大家普遍都认为数字芯片的设计流程更加规范和自动化,不过这几年模拟芯片设计也在向设计流程规范化和自动化方向演进。随着16nm及以下工艺节点的要求越来越严格,这就要求模拟电路设计流程也需要规范化和自动化。

对于模拟设计来说,最难的是Spec的管理。Cadence从前年开始,跟国内很多企业合作,推出了一个ADE(Analog Design Environment;模拟设计环境 ) Verifier工具,该工具也可以称为ADE Planner,是一个模拟设计项目的规划管理工具。

作为一个模拟设计工程师,在一个项目周期内,通常需要从撰写/阅读客户需求或功能需求开始,最后到测试芯片性能,看其是否达到标准结束。在实际工作中,芯片测试的工作大多数时候是由测试工程师完成的,而模拟设计工程师则需要负责芯片的验证,即通过电路仿真工具搭建的Test Bench,看设计出来的电路是否满足产品需求中的要求。

在这个过程中,由两个重要的指标:一是产品需求中的指标(Spec)都被验证了吗(覆盖率)?二是验证都通过了吗(通过率)?解决这两个问题后,还需要知道Test Bench中的Spec设置和产品需求中的Spec是否一致,因为在电路设计过程中,经常会碰到Spec改动的事情。

栾志雨解释说,如果使用ADE Verifier对模拟设计项目进行管理,就能够很清楚地看到,哪些Spec是通过验证了的,哪些是没有通过验证的,以及哪些还需要进一步分析的,一目了然。

对模拟设计而言,还有一个问题就是物理实现。其实模拟电路也是可以拆分的,拆分成一些更小的电路结构。比如现在的代工厂就会基于此类结构,提供一些已经经过测试,良率可以达到一定保障的版图,供模拟芯片设计公司选用。

栾志雨在演讲中表示,这类版图有很多就是使用Cadence的参数化单元Pcell工具来实现的。模拟设计工程师在进行版图设计的时候,如果电路很大,就需要画很多不同尺寸的MOS管,工作会变得很繁琐。而如果使用Cadence最近推出的PcellDesigner工具开发就方便很多,当需要画一个MOS管时,只要调用出Pcell,在其属性中填入所需要的参数(W、L、Gate number等等),就能方便地得到想要的MOS管。这样可以避免单元的重复创建,大大减轻单调乏味的创建图形工作。

他还特意指出,现在使用PcellDesigner还可以开发SuperPcell,将更加方便。SuperPcell指的是客户可以用Coding的方式实现做LDO、或者是运放,这样工程师在调参数的时候就会非常容易。

传统的模拟设计都是从底层到顶层来进行设计的,但在先进工艺节点阶段,这种设计流程会有一些问题。特别是在绕线资源和版图资源相当紧张的时候,因此,客户希望能够有从顶层到底层的设计流程来进行模拟芯片设计。因为从顶层开始设计,能够帮助工程师在顶层、模块层和单元层更为有效地进行规划。

Cadence新推出的Design Planner工具可以为成熟工艺节点和高工艺节点的版图设计提供先进方法,实现无缝衔接版图-布局-布线的功能。同时,它也能够嵌入到数字设计当中,与数字设计同时进行。它具有的创新功能有:

层次化原理图驱动版图设计:结合了自上而下与自下而上设计方法的优势,避免单独使用任意一种设计方法时而引起的缺陷;

层次可视化:用户可在其设计阶段随时随地根据需求轻松地查看或隐藏设计细节,便于仅查看其所需的内容;

层次及拥塞意识的布局及摆放:提供自动化和辅助生产力;

层次化布线和拥塞分析:提前提供真实的路布线及拥塞分析信息。

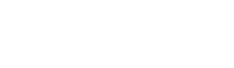

图2:电子和系统设计发展趋势。

In-Design嵌入

In-Design概念是在28nm时提出的,原因是随着工艺节点越来越高,很多芯片是迭代研发设计的,有时候前一代芯片设计验证是没有问题的,迭代后的设计在后端仿真时会出现问题。In-Design就是把后端需要仿真的效应,比如LDE效应、寄生效应、EM效应等都在前端仿真时实现,以方便在流程中提前发现问题,提前预防和解决。

比如Cadence的Pre_EM check就可以提前做EM仿真,发现EM问题。栾志雨指出,其实相对布线造成的EM问题,device层的EM问题对后端的影响更大。因为布线造成的EM问题可以通过修改版图,或者增加线宽等一些局部的修改来解决,而Device层的EM问题很难从后端进行修改,必须修改Device的尺寸,而修改尺寸会导致版图出现问题。

那如何在前端的时候就发现Device层面的问题呢?Pre_EM check就可以帮忙解决。

当然,前仿真不仅针对EM,也可以对LDE效应,EAD效应,以及布线的影响进行检查。提前发现问题,以做出应对方案。

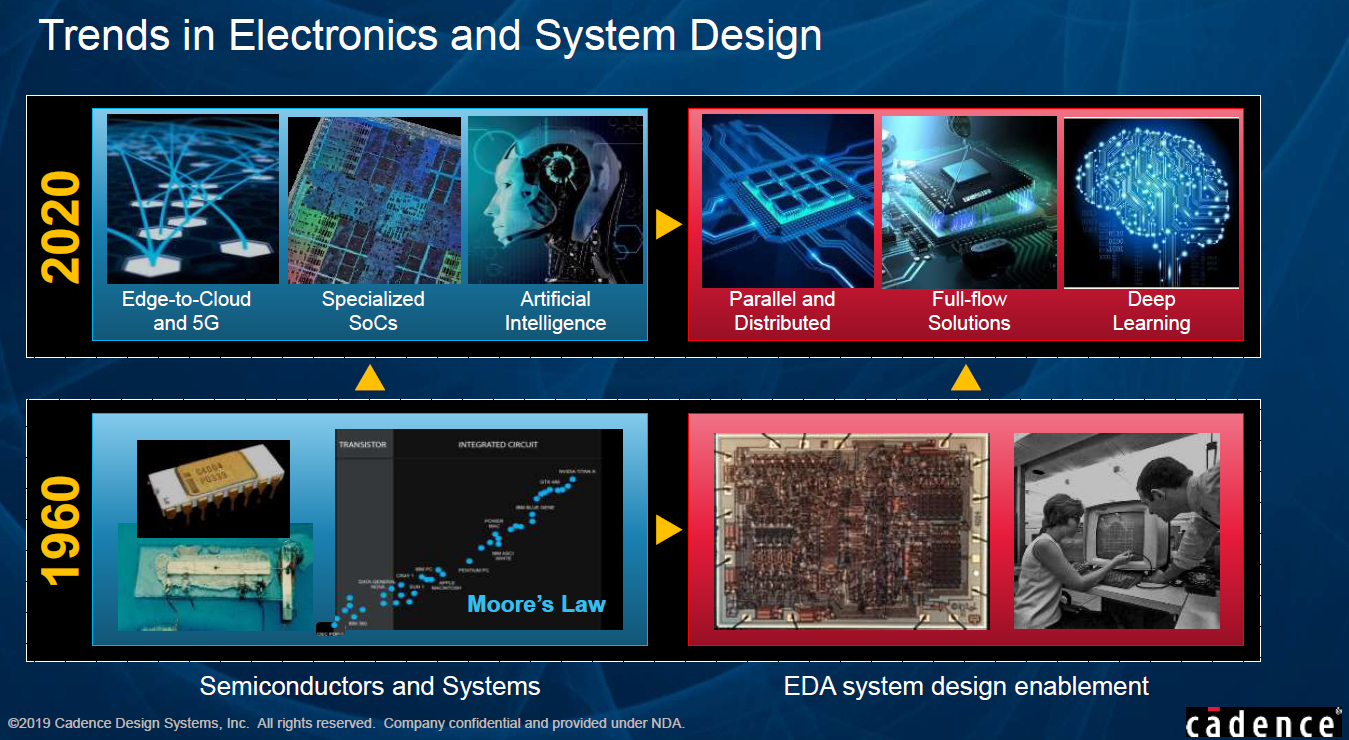

多系统结合

近年来,芯片的设计和系统的结合越来越紧密。传统的模拟设计IP,或者是STA是一个黑盒子,而Cadence最新的Liberate AMS让模拟的STA不再是黑盒子了。AMS基于MX经证明的技术,具有激励表驱动流程、自动侦测setup/hold约束、动态电路分区和静态电路分区等功能。其独有的特点有Deck目录可追溯的特征描述、模拟电路的分区可微调、增强版的激励表接口(可指定model、电压、电流源和电压源等。)、支持内部节点识别,以及支持指定黑盒子单元(比如主动电阻单元、Verilog-A模组等等)。

此外,该工具也可以让模拟的Power不再是一个黑盒子,以及芯片的衬底分析成为可能。

图3:光电一体分析,目前Cadence的EDA工具支持硅光芯片设计和封装实现。

结语

不论是电子设计,还是系统设计,其实一直都在不断演化当中,未来模拟设计的EDA工具也会发生改变,比如说将来一定会有大量的模拟芯片设计是基于云端并行和分布式计算的,模拟芯片的设计会有更加规范化的流程,以及会越来越多地用到机器学习。

阅读下一篇

ARM:从未断供华为 与海思会保持长期合作

在今天举行的ARM和华为的workshop深圳站会议上,两家公司高管对<电子发烧友>表示,ARM和华为一直保持长期合作伙伴的关系,也没有受到美国5月份发布实体名单事件的影响!

返回链料网首页